# PA-RISC 2.0 Firmware Architecture Reference Specification

# **Notice**

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THE MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information that is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated to another language without the prior written consent of Hewlett-Packard Company.

Copyright (C) 1983-2001 by HEWLETT-PACKARD COMPANY All Rights Reserved

# 4. PDC Procedures

The objective of PDC is to provide a uniform, architected context in which to perform processor-dependent operations. One of the two PDC mechanisms is a software entry point which provides a variety of options to execute specific procedures. These procedures access processor-dependent hardware and return parameters that characterize or identify the processor.

PDC stands for Processor-Dependent Code, because the most natural implementation is via PA-RISC code stored in a processor ROM. This does not preclude special hardware support for PDC operations. Any of the PDC procedures may be performed by any combination of code and hardware. In particular, a support processor may be valuable in performing some PDC procedures.

All PDC procedures are provided as options to a single entry point called PDCE\_PROC. PDC is a per processor resource, and operating system software must be prepared to manage separate pointers to PDCE\_PROC for each processor. The address of PDCE\_PROC for the monarch processor is stored in the Page Zero location MEM\_PDC. The address of PDCE\_PROC for each non-monarch processor is passed in GR26 when PDCE\_RESET invokes OS RENDEZ. The procedure options are selected by the value of the index ARG0 in the call to PDCE\_PROC.

#### **ENGINEERING NOTE**

A single copy of PDC may be shared between separate Category B processors, provided semaphores or other similar mechanisms are employed within PDC, so that each processor appears to have its own copy.

The calling conventions for PDC procedures are defined in Section 4.1. Section 4.2 contains a table listing all architected PDC procedures. It is followed by a set of pages giving specifications of the PDC procedures. The procedure pages appear in alphabetical order.

Some of the resources used by PDC procedures are system wide and not per processor. This is specified in the respective PDC procedures. When more than one processor module exists on a system, each processor module must return its associated value for per processor resources. For access to system-wide resources, the same value must be returned no matter on which processor the PDC procedure is called.

For all the PDC procedures there is no change in the architecturally visible module state, except where changes have been specified in the respective PDC procedures and calling conventions.

The architected operation of a module (including execution of PDC) must not require the use of any non-architected PDC procedures. It must also not require the use of any non-architected options in architected PDC procedures.

The converse is also true: the execution of a non-architected PDC procedure (or a non-architected option of an architected procedure) must not affect the architected operation of a module.

PDC procedures must not call IODC entry points.

PDC procedures for PA-RISC 2.0 processors may be called in either narrow (PSW W-bit = 0) or wide (PSW W-bit = 1) mode. Generally OSes which support only 32-bit applications, data, and addressing will call PDC in narrow mode, while OSes that support 64-bit applications, data, and addressing will call PDC in wide mode. The mode of the PDC call is determined by the current W-bit setting at the time of the call. Calls made in narrow mode will use the PA-RISC 1.1 calling conventions, and the PDC procedures will return the same results as defined for the PA-RISC 1.1 PDC procedures. Calls made in wide mode will use the PA-RISC 2.0 calling conventions, and the PDC procedures will return 64-bit results. Details of the PA-RISC 2.0 calling conventions and functional descriptions of the PA-RISC 2.0 PDC procedures follow in this chapter. This information is presented in a format that does not require the reader to be familiar with PA-RISC 1.1 conventions and specifications.

There is one exception to the general rule of PA-RISC 2.0 hardware not having an affect on PA-RISC 1.1 procudure calls. This exception is PDC\_PIM. The memory layout of the buffer pointed to by *memaddr* has been expanded to allow full 64-bit entities (registers and addresses) to be returned, even when PDC is running in narrow mode.

# 4.1 Calling Conventions

The PDC procedures provide a procedural interface to module-type dependent code for processors. The calling convention used for these procedures is a subcase of the one defined in **64-Bit Runtime Architecture for PA-RISC 2.0** by Cary Coutant of California Language Lab. This calling convention allows high level language code to call PDC.

The applicable portions of the calling convention are summarized here; refer to Cary's paper for details. This subset of the calling convention used by PDC is frozen in the I/O Architecture. Indirect calls through special stubs will be required if the convention changes in the future.

In addition to the specific conventions listed in the following sections of this chapter, all PDC procedures which are called while the OS is in control of the system should be loaded into and run from memory. Only the PDC entry points which are triggered by a hardware event should be executed from ROM in I/O space. In addition, code which is run from I/O space should not execute PTLB instructions, as this could cause a system hang.

These calling conventions do not apply to the PDC entry points triggered by TOC, reset, or machine checks.

## 4.1.1 Processor State

The processor must be in the following state when PDC procedures are called:

- The processor must be at Privilege Level 0 at entry, during the PDC procedure call, and at exit.

- The Interruption Vector Table (IVT) is defined by the caller at entry. PDC procedures must not write to the IVT. When the PDC procedure is exited, the IVT must have the same value it had when the procedure was entered.

The following table defines the requirements for the Processor Status Word (PSW) at entry to, during, and at exit from a PDC procedure call. The terms used in the definition of the requirements have the following meaning:

Definition of entry and exit:

Entry Start of the first instruction of the PDC procedure.

Exit Start of the first instruction after return to caller's code.

Terms used to define entry and exit values:

- 0 Must be set to 0 at entry to or exit from the procedure.

- 1 Must be set to 1 at entry to or exit from the procedure.

- C The state of bits marked with C are defined by the caller. If the value at exit is also C, it must be the same as the value at entry.

- X Don't care. On entry, the caller may set these bits to any value. The PDC procedure must not attribute any meaning to the state of these bits. On exit, the PDC procedure may set these bits to any value. The caller must not attribute any meaning to the state of these bits.

Terms used to define allowed actions during execution of the PDC procedure.

Unchanged The PDC procedure must not change these bits from their entry values at any time during execution of the procedure.

Unspecified There are no requirements on the state of these bits. The PDC procedure may modify them as necessary during execution of the procedure.

Restored The PDC procedure may modify these bits as necessary during execution of the procedure, however, they must be restored to their entry value prior to exit from the procedure.

State requirements for the Processor Status Word:

| PSW              | Entry   | During PDC  | Exit    | Name                                    |

|------------------|---------|-------------|---------|-----------------------------------------|

| Bit              | Value   | Execution   | Value   |                                         |

| $\overline{S^1}$ | С       | Unchanged   | С       | Secure Interval Timer                   |

| T                | 0       | Unchanged   | 0       | Taken Branch Trap Enable                |

| H                | 0       | Unchanged   | 0       | Higher Privilege Transfer Trap Enable   |

| L                | 0       | Unchanged   | 0       | Lower Privilege Transfer Trap Enable    |

| $N^2$            | 0       | Unspecified | 0       | Nullify                                 |

| $X^2$            | 0       | Unspecified | 0       | Data Memory Break Disable               |

| $\mathbf{B}^2$   | 0       | Unspecified | 0       | Taken Branch                            |

| C                | 0       | Unchanged   | 0       | Code Address Translation Enable         |

| $V^3$            | X       | Unspecified | X       | Divide Step Correction                  |

| M                | $0^{4}$ | Restored    | $0^{4}$ | High Priority Machine Check Mask        |

| $C/B^3$          | X       | Unspecified | X       | Carry/Borrow Bits                       |

| R                | 0       | Unchanged   | 0       | Recovery Counter Enable                 |

| Q                | 1       | Restored    | 1       | Interruption State Collection Enable    |

| $\mathbf{P}^1$   | C       | Restored    | C       | Protection Identifier Validation Enable |

| D                | 0       | Unchanged   | 0       | Data Address Translation Enable         |

| I                | 0       | Unchanged   | 0       | Ext, P-fail Interrupt, LPMC Unmask      |

| $\mathrm{E}^5$   | 0       | Unchanged   | 0       | Little-Endian Enable                    |

| F                | 0       | Unchanged   | 0       | Performance Coprocessor Enable          |

| $G^6$            | 0       | Unchanged   | 0       | Debug Trap Enable                       |

| $Y^6$            | 0       | Unchanged   | 0       | Data Debug Trap Disable                 |

| $Z^6$            | 0       | Unchanged   | 0       | Instruction Debug Trap Disable          |

| $W^7$            | C       | Restored    | C       | Wide Address Formation Enable           |

| $O_8$            | C       | Restored    | C       | Ordered Memory References               |

#### Notes

- 1. These bits are Defined by the caller. Their value at exit must be the same at their value at entry.

- 2. These bits are changed by normal instruction execution. They will be 0 on entry and exit from the PDC procedure. No action is required by the caller.

- 3. These bits are set by arithmetic instructions during normal execution. No Action is required by the caller.

- 4. Except when PDC\_PIM is called with ARG1=0, in which case the M-bit must be 1.

- 5. Regardless of the endianness of the OS, PDC procedures are defined to run in big endian mode. The OS is responsible for any data swapping and stack management required before and after PDC procedure calls.

- 6. These bits are implemented only on level 0 processors which also implement the debug SFU. In all other cases they are reserved bits.

- 7. The W-bit determines whether PDC is called in wide (64-bit) address mode (W=1), or narrow (32-bit) address mode (W=0). If the W-bit is set to one, the caller must use PA-RISC 2.0 calling conventions. If the W-bit is zero, the caller must user PA-RISC 1.1 calling conventions. If the processor does not implement wide address mode (a PA-RISC 1.1 processor) the W-bit is reserved.

- 8. The O-bit is defined for PA-RISC 2.0 processors only. On PA-RISC 1.1 processors the O bit is reserved.

# 4.1.2 Register State

The following four tables define the requirements for the State of the Control Registers, Space Registers, General Registers, and Floating Point Registers at entry to, during, and at exit from a PDC procedure call. The terms used in the definition of the requirements have the following meaning:

Terms used to define entry and exit state:

- C Defined by the Caller. The value at entry is defined by the caller of the PDC procedure. If the value at exit is also defined by caller, it must be the same as the value at entry.

- HV HVERSION (processor) dependent. The value, if it exists, is dependent on the HVERSION of the processor. It must not be used by the PDC procedure or its caller.

- X Don't Care. On entry, the caller of the PDC procedure may set the register to any value. The PDC procedure must not attribute any meaning to the value. On exit, the PDC procedure may set the register to any value.

The caller must not attribute any meaning to the value.

- U The value of the register is not defined for either the PDC procedure on entry or the caller on exit from the procedure.

- V The value at exit is a result obtained by execution of the PDC procedure.

The terms used to define allowed actions during execution of the PDC procedure are the same for Registers as for PSW bits, with the following additions:

Set Result During the PDC procedure call a result is placed in the register prior to exit.

Unused The PDC procedure is not allowed to write to or rely on the value in the register. However the register may not contain the value at entry during the entire call and at exit.

Register state requirements for Control Registers:

| Entry | During PDC                          | Exit                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Value | Execution                           | Value                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| С     | Unchanged                           | С                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Recovery Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| HV    | Undefined                           | HV                                                                                                                                                                                                                                                                                                                                                                                                                                                         | None (HVERSION Dependent)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| C     | Unchanged                           | C                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Protection IDs 1 and 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| C     | Unchanged                           | C                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Protection IDs 3 and 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| C     | Unchanged/                          | C/V                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Coprocessor Configuration Register/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | Set Result <sup>1</sup>             |                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SFU Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| C     | Unspecified                         | X                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Shift Amount Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| C     | Unchanged                           | C                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Protection IDs 5 and 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| C     | Unchanged                           | C                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Protection ID 7 and 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| C     | Unchanged/                          | C                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Interruption Vector Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | Restored <sup>2</sup>               |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C     | Restored                            | C                                                                                                                                                                                                                                                                                                                                                                                                                                                          | External Interrupt Enable Mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| C     | Unused <sup>3</sup>                 | $C^3$                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Interval Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| U     | Unused                              | U                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Interruption Instruction Address Space Queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| U     | Unused/                             | U                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Interruption Instruction Address Offset Queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       | Unspecified <sup>4</sup>            |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| U     | Unused                              | U                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Interruption Instruction Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| U     | Unused                              | U                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Interruption Space Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| U     | Unused                              | U                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Interruption Offset Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| U     | Unused/                             | U                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Interruption Processor Status Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | Unspecified <sup>4</sup>            |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C     | Unchanged                           | C                                                                                                                                                                                                                                                                                                                                                                                                                                                          | External Interrupt Request Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| C     | Unused/                             | C                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Interruption handler Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | Restored <sup>5</sup>               |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | Value  C HV C C C C C C U U U U U C | Value Execution  C Unchanged HV Undefined C Unchanged C Unchanged C Unchanged C Unchanged C Unspecified C Unspecified C Unchanged C Unchanged C Unchanged C Unchanged C Unchanged Unchanged Unchanged Unused | Value       Execution       Value         C       Unchanged       C         HV       Undefined       HV         C       Unchanged       C         C       Unchanged       C         C       Unchanged/       X         C       Unspecified       X         C       Unchanged       C         C       Unchanged/       C         C       Unchanged/       C         C       Restored       C         C       Unused       U         U       Unused       U         U       Unused       U         U       Unused       U         U       Unused/       U         U       Unused/       U         U       Unchanged       C         C       Unchanged       C         C       Unchanged       C         C       Unchanged       C |

## Notes:

- 1. The only PDC procedure that is allowed to read from or write into the Coprocessor Configuration Register/SFU Configuration Register (CR 10) is PDC\_COPROC. The exit state of CR 10 is either the value at entry, or the value ccr\_functional provided by PDC\_COPROC.

- 2. PDC Procedures may write to the IVA (CR 14) only if they handle their own interruptions. The address of the PDC procedure's interruption handlers is written to CR 14. The caller's interruption handler must be restored before returning to the caller.

- 3. No called PDC procedure is allowed to write to the Interval Timer(CR 16). The value at exit is the value at entry plus the elapsed time of the procedure call.

- 4. PDC procedures may write to CR 18 and CR 22 when it is necessary for them to modify PSW bits. Only the PSW bits to be changed may be written to CR 22. A Return From Interruption (RFI) instruction must be executed as early as possible following the writes to CR 18 and CR 22 to reduce the probability of the value written to these registers by the PDC procedure being destroyed by an interruption.

#### PROGRAMMING NOTE

It is recommended that an RFI instruction immediately follow writes to CR 18 and CR 22.

5. CR 24 through CR 31 are defined for interruption handler use. If a PDC procedure handles its own interruptions, the handler may use these registers for temporary storage. In any case, PDC must restore the original contents before returning to the caller.

Register state requirements for Space Registers:

| SR  | Entry | During PDC  | Exit  |

|-----|-------|-------------|-------|

| No. | Value | Execution   | Value |

| 0-2 | X     | Unspecified | X     |

| 3-7 | C     | Restored    | C     |

Register state requirements for General Registers:

| GR   | Entry | During PDC               | Exit  | Usage                            |

|------|-------|--------------------------|-------|----------------------------------|

| No.  | Value | Execution                | Value |                                  |

| 0    | 0     | Unchanged                | 0     | Zero                             |

| 1    | X     | Unspecified              | X     | Temporary storage (scratch)      |

| 2    | C     | Unspecified <sup>1</sup> | X     | Return Address of caller         |

| 3-18 | C     | Restored                 | C     | Temporary storage (callee saves) |

| 19   | C     | Unspecified              | X     | ARG7                             |

| 20   | C     | Unspecified              | X     | ARG6                             |

| 21   | C     | Unspecified              | X     | ARG5                             |

| 22   | C     | Unspecified              | X     | ARG4                             |

| 23   | C     | Unspecified              | X     | ARG3                             |

| 24   | C     | Unspecified              | X     | ARG2                             |

| 25   | C     | Unspecified              | X     | ARG1                             |

| 26   | C     | Unspecified              | X     | ARG0                             |

| 27   | C     | Restored                 | C     | Defined by caller                |

| 28   | X     | Set Result               | V     | Return Status                    |

| 29   | X     | Unspecified              | X     | Unspecified                      |

| 30   | C     | Restored                 | C     | Caller Stack Pointer             |

| 31   | X     | Unspecified              | X     | Temporary storage (scratch)      |

## Notes:

# Register state requirements for Floating Point Registers:

| FPR  | Entry | During PDC  | Exit                |

|------|-------|-------------|---------------------|

| No   | Value | Execution   | Value               |

| 0    | С     | Unchanged/1 | C/V/HV <sup>1</sup> |

|      |       | Set Result  |                     |

| 1-31 | C     | Unchanged/1 | $C/HV^1$            |

|      |       | Unspecifed  |                     |

## Notes:

1. The floating point registers FPR0 through FPR31 are defined by the caller at entry and must be unchanged by all procedures except PDC\_COPROC. When PDC\_COPROC exits, the values of FPR 0 through FPR 31 are all HVERSION dependent except for the T bit of FPR 0. The T bit of FPR0 returns the test status and must be set to 0 if the test succeeds.

<sup>1.</sup> The PDC Procedure may modify GR 2 as necessary during execution, and the caller may not rely on the contents of GR 2 after the call. The PDC procedure must maintain the value passed in GR2 by the caller to use as a return address after the call completes.

# 4.1.3 Stack Usage

The caller of PDC procedures must provide a doubleword-aligned value in GR 30, the Stack Pointer (SP), which points to the following data:

| SP - 96 |                   |

|---------|-------------------|

| SP - 88 | SAVE_ARG7         |

|         | SAVE_ARG6         |

| SP - 80 | SAVE ARG5         |

| SP - 72 | _                 |

| SP - 64 | SAVE_ARG4         |

| ~- ~ .  | SAVE_ARG3         |

| SP - 56 | SAVE_ARG2         |

| SP - 48 | SAVE ARG1         |

| SP - 40 | SAVE_ARGI         |

| CD 22   | SAVE_ARG0         |

| SP - 32 |                   |

|         | frame marker      |

| SP      |                   |

|         |                   |

|         | temporary storage |

|         | temperary storage |

|         |                   |

|         |                   |

The values of SAVE\_ARG0 through SAVE\_ARG7 are defined by the caller at entry, and are unspecified at exit. They are used to save the first eight arguments to the procedure, which are passed to the procedure in registers GR26 through GR19, respectively. Additional arguments are passed on the stack in successive locations (ARG8 at SP-104, ARG9 at SP-112, ARG10 at SP-120, etc.)

When the called procedure returns, the value of SP must be restored. The memory at the Stack Pointer address SP and the next 7K bytes of larger physical addresses are available for temporary use by the called procedure. If the called procedure is PDC\_POW\_FAIL, the memory at the Stack Pointer address SP and the next 512 bytes of larger physical addresses are available for use by PDC\_POW\_FAIL.

## 4.1.4 Arguments

The procedure to be performed is selected by the index **ARG0**. ARG0 is not explicitly listed in the procedure specifications that follow. The ARG0 value for all PDC procedures is a 64-bit unsigned integer.

The option of the procedure is selected by **ARG1**. For architected PDC procedures, options 0 through 127 are architected or reserved; options (128 through 0xFFFFFFFF) are for HVERSION-dependent use, options above 0x100000000 are reserved. For HVERSION-dependent PDC procedures, all options are for HVERSION-dependent use. The ARG1 value for all PDC procedures is a 64-bit unsigned integer.

Many PDC procedures use the standard argument  $R_{-}addr$  to designate the return parameter buffer. This buffer is a doubleword-aligned block of 32 doublewords allocated by the caller. The procedure can return parameters to its caller by storing into the buffer. If the  $R_{-}addr$  argument is provided, it is always **ARG2**.

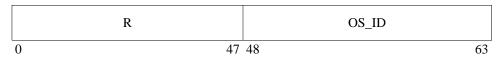

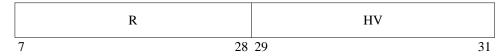

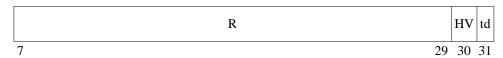

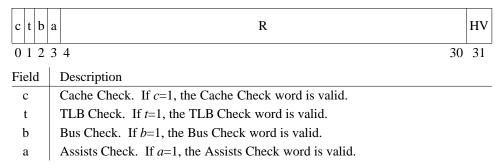

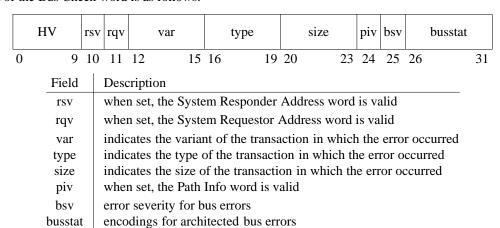

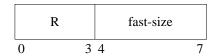

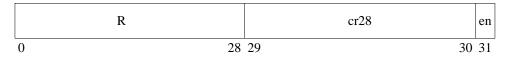

In the procedure specifications that follow, the notation 'R' is used to indicate an argument passed to a PDC procedure which is reserved for future extensions. Reserved arguments must be set by all current callers to 0, and must be ignored by all current callees. Reserved arguments may be architected in the future, with the value 0 defined to preserve compatibility with previous versions.

The notation 'HV' is used to indicate that the value of the argument is not specified by the architecture and so may be freely chosen by the caller. By contrast, arguments denoted by '---' are nonexistent: the caller is not required to provide such arguments at all. Callees must not attach any significance to 'HV' arguments and must not attempt to access '---' arguments.

All address parameters which are passed as arguments or are returned as parameters are 64-bit unsigned integers. The alignment restrictions for these address parameters are specified in each of the PDC procedures.

All signed integers are represented in two's complement (64-bit) format.

#### **4.1.5 Return Parameters**

If a PDC procedure returns parameters to its caller, they are stored in the return parameter buffer specified by  $R\_addr$ . The 32 returned parameters are called RET[0] through RET[31]. At least RET[0] through RET[15] are designated for architected return parameters. Return parameters in RET[16] through RET[31] which are not architecturally defined may be used for HVERSION-dependent purposes. All return parameters neither architected nor used for HVERSION-dependent purposes must be set to 0 by the PDC procedure upon return. The notation 'R' indicates a return value that must be set to 0 by the PDC procedure. The notation '---' indicates that the PDC procedure does not return any parameters.

If a PDC implementation defines a new dependent return word for a procedure, the value 0 must be used to indicate "not implemented" to preserve compatibility with previous versions.

For HVERSION-dependent PDC procedures and HVERSION-dependent options of architected PDC procedures, all 32 return values (RET[0] through RET[31]) are HVERSION dependent.

## **4.1.6 Status**

The status of PDC procedures is returned as a 64-bit two's complement signed integer value in register GR28.

The rest of this section applies only to architected options of architected PDC procedures. For HVERSION-dependent PDC procedures and HVERSION-dependent options of architected PDC procedures, all status values are HVERSION dependent.

The following status values have the same meaning for all PDC procedures to which they apply:

| Value | Description                        |

|-------|------------------------------------|

| 3     | Call completed with a warning      |

| 0     | OK                                 |

| -1    | Nonexistent procedure              |

| -2    | Nonexistent option                 |

| -3    | Cannot complete call without error |

| -10   | Invalid argument                   |

| -12   | BUS_POW_WARN assertion detected    |

Note that status -1 is actually returned by PDCE\_PROC, the entry point for all PDC procedures, rather than by the individual PDC procedures themselves.

Positive status values (values from 1 to 0x7FFFFFFF FFFFFFFF) are used to report advisory information whose meaning is dependent on the procedure that was called.

The other negative status values (values from -4 to -9 and -11 to

-0x80000000 00000000) are used for errors whose meaning is dependent on the procedure that was called.

Status values other than those listed for a PDC procedure are reserved. Each PDC procedure may return only the values specifically defined for it. Reserved values can be assigned architected meanings in the future. Therefore, callers must treat the reserved negative values the same as -3 (Cannot complete call without error) and the reserved positive values the same as 0 (OK).

Some status values are marked as REQUIRED. This means that all implementations of the PDC procedure are required to detect the condition specified by the status value and to return the status value whenever the condition is detected. Values are designated as required when necessary to support the functionality of the procedure.

Some status values are marked as OPTIONAL. This means that each implementation of the PDC procedure can choose whether or not it will detect the condition specified by the status value.

Some status values are marked as CONDITIONAL. These values are accompanied by a specification of the cases in which the condition must be detected and reported. There will be some PDC implementations for which those

cases do not apply; they must not use the given value at all.

#### **ENGINEERING NOTE**

It is expected that those PDC implementations that are able to detect optional conditions will do so (and will return the appropriate status value).

PDC implementations are encouraged to recognize as many specific error conditions as they can.

If an implementation cannot isolate an error to one of the more specific conditions, then it must report the error by returning the general status value -3 (indicating that an indeterminate error was detected). If it cannot isolate one of the specific advisory conditions, then it must return status 0 for "OK".

For all PDC procedures:

- All RET values are valid with a zero return status.

- All RET values are valid with any positive return status unless specified otherwise in the respective PDC procedure description.

- All RET values are HVERSION dependent with a negative return status.

# 4.1.7 Interruptions

PDC procedures may optionally handle their own interruptions.

If PDC procedures do not handle their own interruptions, the execution of PDC procedures must not cause any Group 3 or Group 4 interruptions. If PDC procedures do not handle their own interruptions, they must not write to CR14 or to CR24 through CR31 during the procedure call.

If PDC procedures handle their own interruptions, they must write to CR 14 during the procedure call to point to their interruption handlers. They may optionally modify the contents of CR 24-31 in accordance with their interruption handlers. The interruption handlers must not modify those registers which the PDC procedures are not allowed to modify.

PDC procedures are not required to recover if they receive an HPMC.

#### **ENGINEERING NOTE**

It is recommended that all PDC procedures be re-entrant to help them recover from an HPMC. The probability of receiving an HPMC during a PDC procedure call is considered sufficiently low that PDC procedures are not required to be re-entrant.

# 4.1.8 Powerfail Warning on Central Bus during PDC Call

In the event of a powerfail warning on the central bus while a PDC call is in progress, the procedure must always return quickly enough so that the caller has the full powerfail budget available. PDC\_CHASSIS and PDC POW FAIL must complete all required actions before returning. All PDC procedures except PDC CHASSIS and PDC POW FAIL have two choices in the event of a powerfail warning on the central bus:

- complete all required actions before returning with the appropriate status

- terminate the call prematurely and return -12

A PDC procedure that returns -12 must be restartable, that is, it can be re-executed by the caller.

# PROGRAMMING NOTE

The recommended calling sequence for restartable PDC procedures follows:

```

while ( 1 ) {

PSW I—bit ← 0;

status ← PDC_xxxxx ( <arguments> );

if (status != -12)

break;

PSW I—bit ← 1;

}

```

# 4.2 PDC Procedures

When PDCE\_PROC is called, the index ARG0 specifies the procedure to be performed, as shown below:

| ARG0    | Mode            | Name                | Description                            |

|---------|-----------------|---------------------|----------------------------------------|

| 0       | R               |                     | Obsolete                               |

| 1       | HV              | PDC_POW_FAIL        | Prepare for powerfail                  |

| 2       | A               | PDC_CHASSIS         | Update chassis display                 |

| 3       | A               | PDC_PIM             | Access Processor Internal Memory       |

| 4       | A               | PDC_MODEL           | Return processor model information     |

| 5       | A               | PDC_CACHE           | Return cache and TLB parameters        |

| 6       | A               | PDC_HPA             | Return processor's HPA                 |

| 7       | A               | PDC_COPROC          | Return coprocessor configuration       |

| 8       | A               | PDC_IODC            | Access a module's IODC                 |

| 9       | A               | PDC_TOD             | Access Time-Of-Day clock               |

| 10      | A               | PDC_STABLE          | Access Stable Storage                  |

| 11      | HV <sup>1</sup> | PDC_NVOLATILE       | Access Non-Volatile Memory             |

| 12      | A               | PDC_ADD_VALID       | Validate address                       |

| 13      | R               |                     | Obsolete                               |

| 14      | R               |                     | Obsolete                               |

| 15      | R               |                     | Obsolete                               |

| 16      | $A^2$           | PDC PROC            | Stop the currently executing processor |

| 17      | $HV^3$          | PDC_CONFIG          | Deconfigure and reconfigure a module   |

| 18      | R               |                     | Obsolete                               |

| 19      | $HV^4$          | PDC_TLB             | Manage hardware TLB miss handling      |

| 20      | HV              | PDC_MEM             | Manage per page memory deallocation    |

| 21      | HV <sup>5</sup> | PDC_PSW             | Manage default PSW bits                |

| 22      | HV              | PDC_SYSTEM_MAP      | Map fixed location IO modules          |

| 23      | $HV^6$          | PDC_SOFT_POWER      | Manage software power control          |

| 24      | HV              | PDC_ALLOC           | Allocate IODC data storage             |

| 25      | A               | PDC_CRASH_PREP      | Prepare I/O System for crash dump      |

| 26      | A               | PDC_SCSI_PARAMETERS | Manage SCSI Initialization Parms       |

| 27-127  | R               |                     | Reserved                               |

| 128-511 | $HV^6$          |                     | HVERSION dependent                     |

| > 511   | R               |                     | Reserved                               |

R the procedure index is Reserved

A the procedure is required by the architecture in all PDC implementations

HV the existence of the procedure depends on the HVERSION of the processor

# Notes:

- 1. Required for processors that provide Non-Volatile Memory; not implemented by other processors.

- 2. Required for Category B processors; not implemented by Category A processors.

- 3. Required for processors that support module deconfiguration; not implemented by other processors.

- 4. Required for processors with hardware TLB miss handlers; not implemented by other processors.

- 5. Required for processors which implement the E-bit or W-Bit; not implemented by other processors.

- 6. Required for processor whose IODC firmware require allocated data storage; not required for other processors.

If an implementation provides a PDC procedure, then it must provide all defined options for that procedure, unless explicitly noted to the contrary under the "**Options**" heading in the specifications that follow.

# PDC\_ADD\_VALID (index 12)

**Purpose:** To determine the correct completion of a READ operation without risking an HPMC.

Arguments: Description ARG1 ARG2

Validate address 0 phaddr

|                | , and | o uddress   O phudu                                                                                                                                                              |

|----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Status:</b> | Value | Description                                                                                                                                                                      |

|                | 3     | Call completed with a warning. An error of unspecified type occurred, but the call completed correctly. OPTIONAL. The procedure need not report warning conditions.              |

|                | 2     | Operation completed with a requestor bus error REQUIRED.                                                                                                                         |

|                | 1     | Operation completed with a requestor bus error REQUIRED.                                                                                                                         |

|                | 0     | OK (Operation completed without bus error) The call completed normally and the procedure detected no error. REQUIRED.                                                            |

|                | -2    | Nonexistent option ARG1 did not correspond to an option provided by the procedure. REQUIRED.                                                                                     |

|                | -3    | Cannot complete call without error An error of unspecified type prevented the call from completing correctly. CONDITIONAL. Must be used if indeterminate errors can be detected. |

|                | -10   | Invalid argument An argument other than ARG0 or ARG1 was invalid.  OPTIONAL. The procedure need not check arguments for correctness.                                             |

|                | -12   | Assertion of BUS_POW_WARN signal detected                                                                                                                                        |

#### **Description:**

The "Validate address" option (ARG1=0) allows the caller to determine if a READ to *phaddr* would generate a requestor bus error without risking an HPMC. PDC\_ADD\_VALID generates a READ operation by issuing a load instruction to *phaddr*. The *phaddr* argument is a doubleword-aligned, 64-bit physical address.

CONDITIONAL. Must be used if the procedure cannot satisfy the powerfail budget.

PDC\_ADD\_VALID must return either 1 or 2 when detecting an HPMC fault condition caused by a requestor bus error. PDC\_ADD\_VALID may return either status value, so the caller must check for both values. It must also return one of these values when called for a deconfigured molule which does not normally assert PATH\_SLAVE\_ACK in that state.

For processors that do not implement the full 64-bit address space, PDC\_ADD\_VALID must perform a simple address comparison to check that *phaddr* is within the implemented address space. PDC\_ADD\_VALID must not try to determine the validity of a given physical address by attempting a READ before this test is successful. If *phaddr* is in the unimplemented portion of the address space, PDC\_ADD\_VALID must return either 1 or 2.

If PDC\_ADD\_VALID detects an HPMC condition other than a requestor bus error, it is required to return one of the following status values: 2, 1, 0, or -3. Status value 0 indicates that the HPMC condition did not interfere with the completion of the READ operation. Status value -3 indicates that the HPMC condition interfered with the completion of the READ operation (that is: PDC\_ADD\_VALID could not determine that the read to *phaddr* completed). Status values 1 or 2 may optionally be used when an HPMC condition occurs other than a requestor bus error.

PDC\_ADD\_VALID may optionally enter its caller's HPMC handler when detecting an HPMC condition other than a requestor bus error.

# PDC\_ADD\_VALID (index 12) (continued)

#### **SUPPORT NOTE**

Implementations of PDC\_ADD VALID are encouraged to use status values 0 or -3 for HPMC condtions other than requestor bus errors. Support organizations will decide whether or not an implementation is allowed to use the status values 2 or 1 for these HPMC conditions. This decision is based on the supportability, reliability, and availability requirements of the particular product.

## PROGRAMMING NOTE

Calls to PDC\_ADD\_VALID may cause soft errors to be logged in the lower ports of bus converters involved in the READ operation. Therefore, the caller may wish to issue a CMD\_CLEAR to any bus converter ports that may have been affected. Issuing CMD\_CLEAR is optional, but future error isolation is hampered by having bus converter ports with residual soft errors logged during prior calls to PDC\_ADD\_VALID.

# PDC\_ALLOC (index 24)

**Purpose:** To allocate static data storage for IODC use.

| <b>Arguments:</b> | Description         | ARG1 | ARG2   | ARG3     | ARG4          | ARG5     |

|-------------------|---------------------|------|--------|----------|---------------|----------|

|                   | Allocate Storage    | 0    | R_addr | Size     | High_mem_flag | AllocPtr |

|                   | Get Allocation Ptr  | 1    | R_addr | R        | R             | R        |

|                   | Free Storage        | 2    | R_addr | Address  | R             | R        |

|                   | Free Tagged Storage | 3    | R_addr | AllocPtr | R             | R        |

|                   | Free All Storage    | 4    | R_addr | R        | R             | R        |

Returns: Description RET[0]

Allocate Storage Storage\_address

Get Allocation Ptr AllocPtr

| <b>Status:</b> | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|