# **Standard Text Interface** For Graphics Devices

Revision 8.13 March 1, 2000

## Notice

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THE MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information that is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated to another language without the prior written consent of Hewlett-Packard Company.

Copyright © 1983-1999 by HEWLETT-PACKARD COMPANY All Rights Reserved

## Table of Contents

| 1 | PURPO            | DSE                                                                                   | 1    |

|---|------------------|---------------------------------------------------------------------------------------|------|

|   | 1.1 USA          | GE                                                                                    | 1    |

|   |                  | UMPTIONS                                                                              |      |

|   |                  | ECTIVES                                                                               |      |

|   |                  | NS FOR ACHIEVING OBJECTIVES                                                           |      |

|   |                  |                                                                                       |      |

| 2 | DEFIN            | ITIONS                                                                                | 7    |

|   | 2.1 Gra          | PHICS                                                                                 | 7    |

|   | 2.1.1            | Frame Buffer                                                                          | 7    |

|   | 2.1.2            | Control Space                                                                         | 7    |

|   | 2.1.3            | Privileged Space                                                                      |      |

|   | 2.2 Syst         | rems                                                                                  | 7    |

|   | 2.2.1            | SPU                                                                                   | 7    |

|   | 2.2.2            | Boot ROM                                                                              | 7    |

|   | 2.2.3            | Kernel                                                                                | 7    |

|   | 2.3 Bus          |                                                                                       | 8    |

|   | 2.3.1            | <i>SGC</i>                                                                            | 8    |

|   | 2.3.2            | <i>GSC</i>                                                                            | 8    |

|   | 2.3.3            | <i>PCI</i>                                                                            | 8    |

|   | 2.3.4            | Other                                                                                 | 8    |

|   | 2.4 ENI          | DIAN                                                                                  | 8    |

|   | 2.4.1            | Big Endian                                                                            | 9    |

|   | 2.4.2            | Little Endian                                                                         | 9    |

|   | 2.5 Nom          | IENCLATURE                                                                            | . 10 |

| 3 | OVER             | VIEW                                                                                  | . 11 |

|   |                  | ROM STRUCTURE                                                                         |      |

|   |                  | A Format                                                                              |      |

|   |                  |                                                                                       |      |

|   | 3.3 USA<br>3.3.1 | GE CONSIDERATIONS                                                                     |      |

|   | 3.3.1<br>3.3.2   | Byte Mode ROM in low address<br>PCI Expansion ROM Support                             |      |

|   | 3.3.2<br>3.3.3   | PCI Expansion ROM Support                                                             |      |

|   | 3.3.4            | PCI Speed and Size                                                                    |      |

|   | 3.3.4            | SGC                                                                                   |      |

|   | 3.3.6            | GSC                                                                                   |      |

|   | 3.3.7            | HP-UX 32 and 64 bit OS                                                                |      |

|   |                  |                                                                                       |      |

| 4 | ROM.             |                                                                                       | . 15 |

|   | 4.1 BYT          | E, WORD AND PCI FORMATS                                                               | 15   |

|   | 4.1.1            | BYTE MODE                                                                             |      |

|   | 4.1.2            | WORD MODE                                                                             |      |

|   | 4.1.3            | PCI                                                                                   |      |

|   | 4.1.3            |                                                                                       |      |

|   | 4.1.3            | .2 Details of a single ROM image                                                      | 18   |

|   | 4.1.3            |                                                                                       |      |

|   |                  | 1.3.3.1 Header – PCI Architected                                                      |      |

|   |                  | 1.3.3.2       ROM Type – HP Unique         1.3.3.3       STI Image Offset – HP Unique |      |

|   | 4.               | 1.3.3.3 STI Image Offset – HP Unique                                                  |      |

|   | 4.              | 1.3.3.4 ROM Size – HP Unique                         |    |

|---|-----------------|------------------------------------------------------|----|

|   | 4.              | 1.3.3.5 PCI DS Offset – PCI Architected              |    |

|   | 4.              | 1.3.3.6 PCI Region Mapper Offset – HP Unique         | 21 |

|   | 4.              | 1.3.3.7 PCI Data Structure – PCI Architected         | 22 |

|   | 4.1.3.          | .4 PCI dual EROM mapping                             | 23 |

|   | 4.1.4           | Aberrations                                          | 23 |

|   | 4.1.4.          | 1 Column mode                                        | 23 |

|   | 4.1.4.          |                                                      |    |

|   | 4.2 STU         | Image Format                                         |    |

|   | 4.2.1           | General                                              |    |

|   | 4.2.2           | DD Struct Field Descriptions                         |    |

|   | 4.2.2           |                                                      |    |

|   | 4.2.2.          |                                                      |    |

|   |                 |                                                      |    |

|   | 4.2.2.<br>4.2.2 | 8                                                    |    |

|   |                 |                                                      |    |

|   | 4.2.2.          | 81                                                   |    |

|   | 4.2.2.<br>4.2.2 |                                                      |    |

|   |                 | 8                                                    |    |

|   | 4.2.2.          |                                                      |    |

|   |                 | 2.2.8.1 crc depends on ROM an even multiple of bytes |    |

|   | 4.2.2.          |                                                      |    |

|   |                 | 2.2.9.1 Block TLBs                                   |    |

|   | 4.2.2.          |                                                      |    |

|   | 4.2.2.          |                                                      |    |

|   | 4.2.2.          |                                                      |    |

|   | 4.2.2.          |                                                      |    |

|   | 4.2.2.          |                                                      |    |

|   | 4.2.2.          |                                                      |    |

|   | 4.2.2.          |                                                      |    |

|   | 4.2.2.          | rr                                                   |    |

|   | 4.2.2.          | 11                                                   |    |

|   | 4.2.2.          | 51                                                   |    |

|   | 4.2.2.          |                                                      |    |

|   | 4.2.2.          |                                                      |    |

|   | 4.2.3           | mon tbl descriptor strings                           |    |

|   | 4.2.4           | User Data                                            |    |

|   | 4.2.5           | Overlay Routines                                     | 42 |

|   | 4.2.6           | Regions                                              |    |

|   | 4.2.7           | Device Dependent Routines                            |    |

|   | 4.2.8           | Font Storage                                         |    |

|   | 4.2.8           | 0                                                    |    |

|   | 4.2.8           | •                                                    |    |

|   | 4.2.8           |                                                      |    |

|   |                 | AILED EXAMINATION                                    |    |

|   |                 |                                                      |    |

|   | 4.3.1           | PCI                                                  |    |

|   | 4.3.2           | Word Mode                                            |    |

|   | 4.3.3           | Byte Mode                                            | 55 |

| F | DOUT            | INES                                                 | 57 |

| 5 | ROUII           | UNEO                                                 |    |

|   | 5.1 GENE        | ERAL                                                 | 57 |

|   | 5.1.1           | calling conventions                                  |    |

|   | 5.1.1           | 0                                                    |    |

|   |                 | busy waiting and reentrancy                          |    |

|   | 5.1.3           | memory usage                                         |    |

|   | 5.1.4           | error returns                                        |    |

|   | 5.1.5           | end address                                          | 62 |

|   | 5.1.6           | Global Config                                        | 63 |

|   |                 | GRAPH                                                |    |

|   |                 | E MANAGEMENT                                         |    |

|   |                 | E MANAGEMENT                                         |    |

|   | J.H FUNI        |                                                      |    |

|   | 5.5  | BLOCK MOVE                                      | 75   |

|---|------|-------------------------------------------------|------|

|   | 5.6  | SELF TEST                                       | . 78 |

|   | 5.7  | EXCEPTION HANDLER                               | 80   |

|   | 5.8  | INQUIRE CONFIG                                  | 86   |

|   | 5.9  | SET CM ENTRY                                    |      |

|   | 5.10 | DMA CTRL                                        | . 90 |

|   | 5.11 | FLOW CTRL                                       | . 92 |

|   | 5.12 | USER TIMING                                     | . 96 |

|   | 5.13 | PROCESS MGR                                     | . 97 |

|   | 5.14 | STI UTIL                                        | 100  |

| 6 | U    | SAGE                                            | 103  |

|   | 6.1  | ROUTINE USAGE CONSIDERATIONS                    | 103  |

|   | 6.2  | BOOT ROM USAGE.                                 |      |

|   | 6.3  | KERNEL USAGE                                    |      |

|   |      | 3.1 iomap                                       |      |

|   |      | 3.2 gcmap                                       |      |

|   | 6.4  | MILLICODE                                       |      |

|   | 6.5  | FLOATING POINT USAGE                            |      |

|   | 6.6  | USER SPACE USAGE                                |      |

|   |      | 6.1 Sample Util usage                           |      |

|   | 0.   | 6.6.1.1 User Code                               |      |

|   |      | 6.6.1.2 STI Code                                |      |

|   | 6.   | 6.2 Sample DMA usage                            | 124  |

|   |      | 6.6.2.1 User Code                               | 124  |

|   |      | 6.6.2.2 STI Code                                | 126  |

|   | 6.7  | MULTIPLE ROUTINES                               |      |

|   | 6.8  | FREQUENCY REFERENCE.                            | 138  |

|   | 6.9  | EXTRA MEMORY                                    |      |

|   | 6.10 | IMPLICIT LOCKING VS. EXPLICIT LOCKING           | 139  |

|   | 6.11 | CFB                                             |      |

|   | 6.12 | VGA SUPPORT                                     |      |

|   | 6.13 | VM STI                                          | 140  |

|   | 6.14 | MULTIPLE MONITORS                               |      |

|   | 6.   | 14.1 User Data Space                            |      |

|   | 6.15 | EARLY CONSOLE (AKA FRIENDLY BOOT )              |      |

|   | 6.16 | MULTIPLE FONTS                                  |      |

|   | 6.17 | TERMCAP                                         |      |

|   | 6.18 | IODC SV - FIRMWARE INFO                         | 144  |

| 7 | A    | PPENDIX                                         | 145  |

|   | 7.1  | 64 BIT ID                                       | 145  |

|   | 7.2  | COMPATIBILITY BETWEEN REVISIONS                 |      |

|   | 7.3  | CRC ALGO                                        |      |

|   | 7.4  | HEADER FILES                                    | 147  |

|   | 7.4  | 4.1 sti.h                                       | 147  |

|   |      | 4.2 errno.h - device common error codes         |      |

|   |      | 4.3 local_errno.h - device specific error codes |      |

|   | 7.5  |                                                 |      |

|   |      | 5.1 Romalizer                                   |      |

|   | ,    | 5.2 <i>Fakedrive</i>                            |      |

|   |      | 5.3 Other                                       |      |

|   | 7.6  | ORDERED LIST OF CHANGES                         |      |

|   |      |                                                 |      |

# Table of Figures

| Figure 1 – Big Endian                              | 9  |

|----------------------------------------------------|----|

| Figure 2 – Little Endian                           | 10 |

| Figure 3 - Byte Mode ROM                           | 16 |

| Figure 4 - Word Mode ROM                           | 17 |

| Figure 5 - PCI ROM Image                           |    |

| Figure 6 - STI Image in PCI Rom                    |    |

| Figure 7 - PCI Header in Little Endian Format      |    |

| Figure 8 - PCI Region Mapper for STI               | 21 |

| Figure 9 - PCI Data Structure                      |    |

| Figure 10 - STI ROM Structure                      | 25 |

| Figure 11 – DD Info Structure                      |    |

| Figure 12 – Routine Structure                      | 27 |

| Figure 13 – Alternate Routine Structure            |    |

| Figure 14 - DD Structure                           |    |

| Figure 15 – HP-UX Region Usage                     |    |

| Figure 16 - DD Routine Pointers for PA-RISC Code   | 46 |

| Figure 17 - DD Routine Pointers for Alternate Code |    |

| Figure 18 - Font Structure                         | 51 |

| Figure 19 - Font Types                             |    |

|                                                    |    |

## 1 Purpose

The purpose of this document is to define and explain the format and functionality of the STI ROM in enough detail to allow STI developers and those who need to interface to graphics devices to make their contributions efficiently and correctly.

The purpose of the STI itself is to provide a means whereby the SPU Boot ROM and Operating System can perform the graphics device dependent text operations and self test without having specific device dependent information. Instead, the device dependent information is contained in code supplied in the STI ROM. A much more detailed set of objectives is listed below.

Note that the first products using STI were released in 1990 and the original STI specification was also released in 1990. The last revision to the STI specification was made in 1991. There have been numerous additions to the STI capability since that time and this revision attempts to bring the STI specification up to date.

Editorial comments have been added, and are shown in italic, where there is a difference in the original specification and this revision. This is mostly the case for some of the comments that have been dated by new hardware additions.

#### 1.1 Usage

STI has three primary modes of usage:

- 1. Boot console support. The Boot ROM (SPU system firmware) uses STI in a device independent manner to display boot time messages. In PC type boxes this type of functionality has been provided by the combination of VGA hardware and the VGA Bios.

- 2. OS console support. The Operating System also uses STI in a device independent manner to display system messages. When a graphics card is used to display console messages, STI is the mechanism that is used.

- 3. OS runtime support. The Operating System also uses STI for runtime support to provide services to users of the graphics device, as well as its own use. A primary example of users of the graphics device is the X11 server and an example of the Operating System runtime use is interrupt support.

#### 1.2 Assumptions

Several assumptions have been made about what type of devices will use the Standard Text Interface.

These assumptions include:

• All devices will be bitmapped graphics devices. This implies that none of the devices necessarily have separated, dedicated alpha and graphics planes although some planes may tend to be used primarily for text.

Note that other, non-graphics devices, have used the STI concept. It turns out that STI is useful in the development of new hardware. It has been used many times to quickly add devices for prototyping purposes.

- Off screen memory will not necessarily be available.

- If offscreen display is available, it will be to the right and/or below the onscreen display.

- The device will not necessarily support hardware block moves although the STI ROM must still provide a block move routine, even if it requires the use of sequential reads and writes to do the block move.

- The frame buffer configuration can vary significantly from device to device.

- Color may or may not be supported.

- Only merged 680X0 and PA-RISC SPU platforms will be supported.

Note that Motorola based HP Workstations production ended many years ago. The original specification covered both the 68000 family and the PA-RISC family of HP Workstations.

• HP-UX and Domain, and possibly OSF Operating Systems will be supported.

Note that many other Operating Systems have been ported to use STI. HP-UX, which is the Hewlett-Packard implementation of UNIX was and still is the primary user of STI. Domain was the Operating System used by the Apollo brand computer that Hewlett-Packard acquired in the early 1990s. STI has also been used by HP-RT, the HP Real Time OS. Other Operating Systems that have used STI are FreeBSD, NextStep and Mach, and there is currently a port of Linux to PA-RISC that is using STI.

• No microcode will be used by the STI routines to support the necessary functionality.

The intent was not to limit STI usage of microcode, but to not require a user of STI to manage microcode supplied by STI. STI has been used with hardware that required microcode, but STI controlled the microcode download to the hardware, transparent to the user of the STI routines.

## 1.3 **Objectives**

Musts:

- Provide a mechanism whereby the SPU can initialize the graphics device to a known state and determine device configurable characteristics (e.g. frame buffer size).

- Provide an interfacing mechanism for all SGC cards, which will work without change in any SPU that supports SGC. (PA-RISC and 68000).

The original bus in the PA-RISC and 68000 workstation products was SGC but STI has since been used with many hardware and bus architectures.

- Insure that the overall system cost that the interfacing mechanism generates is minimized.

- Provide a mechanism that will continue to be usable for products that will be developed in the next 2-3 years.

STI has been in use for over 10 years now. The architecture provided by STI turned out to be highly extensible and very flexible.

• Insure that the schedules of SGC products currently under development are not adversely affected by the solution.

We were developing the STI architecture simultaneously with the first version of PA-RISC workstation hardware. Obviously we wanted to make sure that we did not impact product delivery schedules.

- Provide a mechanism whereby the SPU can easily determine what type of graphics device, if any is in each slot.

- Provide a mechanism whereby the SPU Boot ROM can use the device as system console and communicate with the user via text output to the graphics device.

- Provide an interfacing mechanism such that the existing releases of the SPU Boot ROM can perform the necessary text operations to new graphics hardware without any changes (after initial STI release) to the Boot ROM. (De-couple STI/Boot ROM releases).

This was the primary motivation behind STI. Prior to the invention of STI, new graphics that were developed for both new and existing workstations and servers required System Firmware as well as System Kernel changes to support the new graphics hardware. This was a real problem with syncing up the system software and graphics hardware releases.

- Provide a mechanism whereby the SPU Kernel/ITE is able to perform necessary text operations to the graphics device.

- Provide an interfacing mechanism such that the existing releases of the Kernel/ITE can perform the necessary text operations to new graphics hardware without any changes (after initial STI release) to the Kernel/ITE. (De-couple HW/SW releases).

This was the primary motivation behind STI. Prior to the invention of STI, new graphics that were developed for both new and existing workstations and servers required System Firmware as well as System Kernel changes to support the new graphics hardware. This was a real problem with syncing up the system software and graphics hardware releases.

- Insure that all system configurations have available at least one font to support the necessary text operations.

- Provide a mechanism whereby graphics product designers can implement test functionality that will provide the SPU with pass/fail information at the FRU (Field Replaceable Unit) level.

High Wants:

- Minimize the amount of SPU ROM and RAM that the Boot ROM requires in order to use the graphics device as system console.

- Minimize the level of ongoing support needed by the kernel group to provide ongoing support for the ITE.

- Provide a standard text interfacing mechanism for use by other graphics devices in addition to SGC graphics device.

We knew that SGC would be just the first bus implementing graphics and we wanted to make sure that there were no bus specific limitations.

#### 1.4 Plans for achieving objectives

Note that all the comments in this section were retained from the original specification for historical purposes only.

It is believed that the following strategy allows us to best meet the objectives listed above. The strategy focuses on defining and implementing device independent interfaces and minimizing system cost.

Determine which functionality is necessary for the Boot ROM and kernel to use the graphics device.

Of this functionality, determine which is dependent on the characteristics of a particular graphics device and provide it in an STI ROM in the graphics hardware.

Implement the device independent functionality in the SPU such that systems with multiple SGC devices will only incur the cost of such functionality once.

Provide a simple, well defined, device independent interface between the SPU and the graphics device.

Encourage the SPU designers to provide a simple, well defined interface between the ITE and the Boot ROM to minimize duplication of functionality in the SPU.

## 2 **Definitions**

## 2.1 Graphics

Graphics hardware is commonly broken into frame buffer space, which is the memory of the pixels that are displayed on the screen, and control space, which are registers to control the card. STI also creates a space called the privileged space.

#### 2.1.1 Frame Buffer

The frame buffer is where the pixels that are shown on the screen are located.

#### 2.1.2 Control Space

Control space provides for access to registers that control the video card. Examples include video timing registers, etc.

## 2.1.3 **Privileged Space**

The privileged space normally contains control registers that you would not want any user program to touch. One such example would be the reset bit that resets the card. If this was accessible through user space then any user program could reset the card. This could potentially lead to panic of the kernel.

#### 2.2 Systems

Systems consist of the SPU, Boot ROM and the Kernel.

#### 2.2.1 SPU

SPU is the system processing unit. It is an all-encompassing method of describing the box that includes CPU, memory and all other pieces that are normally thought of as the computer system.

#### 2.2.2 Boot ROM

The Boot ROM is the firmware associated with the CPU motherboard that controls all the base system hardware.

#### 2.2.3 Kernel

The Kernel is the core part of an Operating System.

#### 2.3 Bus

Bus defines the connection mechanism between the system and the graphics card.

## 2.3.1 SGC

The Standard Graphics Connection bus, abbreviated SGC, is defined in a separate document A-5960-1585-1. It was defined as a standard interface to connect graphics products to HP workstation hosts.

There were multiple form factors available.

## 2.3.2 **GSC**

The GSC bus was originally known as the Graphics System Connect and later came to be called the Gonzo System Connect, and is defined in a separate document. There were multiple versions including the original GSC, GSC-1X, GSC+, GSC-1.5X and GSC-2X.

The GSC bus is a synchronous, 32 bit I/O bus used in many of Hewlett-Packard's computers. GSC features a multiplexed address/data bus, a parity bit, basic protocol with extensions to meet both workstation and server needs and a data rate up to 256Mbyte/sec.

There were multiple form factors available.

The GSC 1.5X extensions define write coalescing. The usage example would be writes to a graphics device. The processor writes to the graphics FIFO/frame buffer by executing single word or double word store instructions to an I/O space address. Writes are issued to consecutive memory locations, hardware is added that evaluates the addresses and coalesce contiguous transfers into transactions with larger data payloads.

The GSC 2X extensions address the frequency at which data is driven onto the physical bus. The 2X extensions define a protocol whereby the device driving data can switch the data on every rising and falling edge of the GCLK.

## 2.3.3 PCI

The PCI bus is defined by PCI SIG and is currently at revision 2.2 (December 18,1998).

#### 2.3.4 Other

STI is adaptable to other buses and has been used successfully on VME and others, including proprietary non-HP system buses.

#### 2.4 ENDIAN

To be consistent with the SGC specification, the "Motorola" endian interface is used. This means that it has big endian byte and halfword (16 bit) addressing but the bits are numbered little endian. The bus does not support bit addressing and so this is just a matter of convention. Byte transactions are supported and are always aligned to the proper location within the 32-bit word.

## 2.4.1 Big Endian

| Most Significant |        | Least Significant | t      |

|------------------|--------|-------------------|--------|

| Byte 0           | Byte 1 | Byte 2            | Byte 3 |

| 31 24            | 23 16  | 15 8              | 7 0    |

| Halfword 0       |        | Halfword 1        |        |

#### Figure 1 – Big Endian

#### 2.4.2 Little Endian

| Least Significant |        | Most Significant |        |

|-------------------|--------|------------------|--------|

| Byte 3            | Byte 2 | Byte 1           | Byte 0 |

| 31 24             | 23 16  | 15 8             | 7 0    |

| Halfword 1        |        | Halfword 0       |        |

## 2.5 Nomenclature

A "0x" in front of a value indicates the value is a hexadecimal representation (unsigned unless otherwise noted). All other values are assumed to be decimal.

## 3 Overview

#### 3.1 STI ROM Structure

The general structure of the ROM can be broken down into the following sections:

- 1. Device Data

- 2. Routines

- 3. Font Data

- 4. Other Data

The Device Data (DD) section includes the graphics ID, other information and pointers to other functions and sections within the ROM.

The Routines section includes the following routines:

• Initialization Routine (INIT\_GRAPH)

A routine to put the graphics system into an initialized state that will support text output to the device. It will do such things as enable the needed frame buffer planes, setup the color map and return configuration information that can vary from graphics device to graphics device.

• State Management Routine (STATE\_MGMT)

This routine provides the capability to save the current state of the graphics device before it is initialized and then restore this state at some later time.

• Font Unpack/Move (FONT\_UNP/MV)

A routine to unpack a font character out of the font storage space and put it at a (x, y) location in the frame buffer.

• Block Move Routine (BLOCK\_MOVE)

A routine to move a variable size block of data from one (x, y) pixel location in the frame buffer to another. This will be used to move data within the frame buffer. This routine can also be used to clear a variable size block of data within the frame buffer.

• Self-Test Routine (SELF\_TEST)

A routine for testing the device at power-up.

• Exception Handling Routine (EXCEP\_HDLR)

A routine for handling interrupts and bus errors.

• Inquire Configuration Routine (INQ\_CONF)

A routine for providing information about the current configuration of the device. This routine is primarily used in support of the GCDESCRIBE functionality needed by the HP-UX kernel.

• Set Color Map Entry (SET\_CM\_ENTRY)

A routine that allows control of color map entries that is not directly used by STI. This was added to support the "early console" capability.

• DMA Control (DMA\_CONTROL)

A routine for setting up and managing DMA activity to or from the STI based device.

• Flow Control (FLOW\_CONTROL)

A routine for managing the IO transactions to the device. Normally this is for maintaining the high-water and low-water marks associated with buffered devices.

• User Timing (USER\_TIMING)

A routine for allowing user based code to request a reconfiguration of the monitor timing.

• Process Management (PROCESS\_MGR)

A routine to handle unique HP-UX kernel requirements normally used to control implicit locking devices.

• STI Utility (STI\_UTIL)

A routine that provides generic capabilities to user based processes. This is for additional functionality that is not controlled by one of the other STI routines.

The Font Storage area includes all of the appropriate fonts necessary for the proper operation of the device.

The Other area includes items like:

- List of device Regions to map into memory.

- Monitor timing information

- User unique data

## 3.2 ROM Format

In several places in the STI ROM, addresses and/or offsets are stored. These addresses and offsets are all, unless otherwise noted, relative to the start of the STI ROM (which is, almost always, the start of the device's I/O space). These addresses and offset must have the following format unless otherwise noted. They must all be values that contain a count of the number of bytes from the beginning of the STI ROM to the address of interest. In addition, the count must point to the byte that contains the valid data. For example, if we wanted to add a value in the ROM which is the offset to the "Local ROM rev", then this offset would contain the value 0x0f.

Note that the comment about the start of the device's I/O space is not true for PCI based devices. Also the example offset given is for the Byte Mode ROM, which is described later.

Pointers to the various places within the ROM can then be created by adding these offsets to the address of the start of STI ROM space. (See the section on Device Region List for more information on this). These pointers can then be used as byte, half-word or word pointer by the routines as they choose. The users of these pointers must be aware however that using them as half-word or word pointers will probably cause the SPU to do two cycles for the access since the pointer is not aligned to a word or half-word. The user may want to adjust their value for the proper alignment in such cases. In addition, some machines may have harsher restrictions on the type of pointers allowable and their alignment. STI code developers should check with 68000 and PA-RISC experts to get further details.

For consistency, all unused locations must contain zeros. This includes unused bit fields within locations that contain flags. In addition, if a location is defined to contain a pointer to a routine but that routine is not available, the pointer must be set to zero to indicate that the routine does not exist. Hardware designers must not map readable registers on top of unused locations in the ROM as even the unused locations are considered when the CRC is done. Registers can still be mapped over the upper three unused bytes of each location.

Again note that the comment about mapping registers over the upper three unused byte locations pertains to Byte Mode ROM only.

## 3.3 Usage considerations

## 3.3.1 Byte Mode ROM in low address

The STI ROM must reside in the lowest address locations of the graphics device and must contain an even number of bytes.

The graphics device is only allowed to map its ROM onto the least significant byte of each word in its address space. Previous ROM definitions have allowed mappings to bytes, half-words or words. Even with these options most devices have chosen to use only the least significant byte due to the simplification it offers in hardware design.

Because of this mapping scheme, the code provided in the STI ROM is not designed for execution directly from ROM. Rather, it must be loaded into system RAM in a packed format (every fourth byte in ROM becomes contiguous in RAM) and then executed.

## 3.3.2 PCI Expansion ROM Support

PCI based graphics devices can use the PCI Expansion ROM space in addition to the memory mapped I/O space, but they must at least support the PCI Expansion ROM space.

## 3.3.3 PCI Multiple Bar Support

The graphics device, on PCI, can support multiple Bars

## 3.3.4 PCI Speed and Size

All variants of the PCI bus are supported. Currently HP does not have any AGP enabled workstations. Our current workstations support both the 32 and 64 bit PCI address ranges as well as both the 33 and 66 MHz speed selections.

#### 3.3.5 SGC

SGC was only a single speed bus.

#### 3.3.6 **GSC**

GSC has been available at basically two speeds, either 30Mhz or 40Mhz. See the GSC spec for details.

#### 3.3.7 HP-UX 32 and 64 bit OS

Current STI supports both the 32 and 64 bit versions of the HP-UX Operating System.

## 4 ROM

## 4.1 Byte, Word and PCI formats

In PA-RISC systems based on SGC or GSC IO bus there are 4 dedicated spaces for graphics (each of which is 32Mbytes). These spaces are 0xf4000000, 0xf6000000, 0xf8000000 and 0xfa000000. The first two 32Mbyte spaces can be combined into a single 64Mbyte space, and likewise, the second two 32Mbyte spaces can be combined into a single 64Mbyte space. Note that the  $2^{nd}$  and  $3^{rd}$  32Mbyte spaces cannot be combined into a single 64Mbyte space. So in these systems you can have up to 4 separate graphics cards with each requiring a maximum of 32Mbytes or some combination less than 4 cards if one or more require 64Mbytes. If a graphics card does not require the full range (32Mbytes or 64Mbytes) the remaining space is not available for other IO.

For SGC and GSC bus based systems, the STI ROM is architected to live at the beginning of the hardware address space. For example, if you have a graphics card that only requires 32Mbytes and is in a slot that maps the based address of the card to 0xf4000000 then the ROM would start at 0xf4000000. There are no architectural requirements for the size of the ROM. Typically you will find that the ROM ranges in size from 64Kbytes on older hardware to 256Kbytes on newer graphics hardware.

Note that there is a single exception to the rule that the STI ROM lives at the base of the graphics hardware (for SGC and GSC based graphics). The 712/60-80-100, the 715/100 and the 725/100 products had built in graphics (on the GSC bus) that did not have a physical ROM for the graphics firmware. The graphics firmware (STI ROM) was included as part of the base System ROM and the Boot ROM and Kernel were special cased to handle this one exception. All other SGC and GSC based graphics cards have followed the standard with the ROM at the base of the graphics hardware.

Some of the early SPU based on PCI still had the requirement that the STI ROM live at the base HPA of the graphics hardware. Newer systems do not require this because the BOOT ROM and HP-UX kernel have been changed to use the PCI expansion ROM mapping mechanism associated with PCI based systems.

Prior to PCI based systems, STI images were available in two primary formats referred to as BYTE MODE and WORD MODE. The distinction is how the ROM is mapped into the address space.

With the adoption of the PCI Local Bus architecture, a modification to the WORD MODE format was made.

## 4.1.1 BYTE MODE

Byte mode ROMS will be mapped such that the least significant byte in PA-RISC address space is all that is valid. The top three bytes, in a long word read, will not be used. Obviously, you can not execute code out of the BYTE MODE ROM.

The following figure shows how the least significant byte is mapped into PA-RISC memory mapped IO space. The area in gray depicts the valid data for each long word address.

| Byte 0 | Byte 1 | Byte 2 | Byte 3 | Address |

|--------|--------|--------|--------|---------|

| ?      | ?      | ?      | 0x11   | 0x0     |

| ?      | ?      | ?      | 0x22   | 0x4     |

| ?      | ?      | ?      | 0x33   | 0x8     |

| ?      | ?      | ?      | 0x44   | 0xc     |

| ?      | ?      | ?      | 0x55   | 0x10    |

|        |        |        |        |         |

| ?      | ?      | ?      | 0x66   | end Rom |

Figure 3 - Byte Mode ROM

Note that in the figure if you perform a long word read of address 0x0 you would get 0x??????11 where the ?? is indeterminate data because only the least significant byte is valid.

For some hosts, the low byte will be duplicated to the other 3 byte positions and for other hosts it is whatever the bus termination provides. Still yet other hosts might drive out whatever was last latched in the bus transceivers.

## 4.1.2 WORD MODE

Word mode ROMS map all four bytes into the PA-RISC address space so that a user does not have to read 4 bytes and pack them into a word in order to execute a single instruction. Based on this you could actually execute out of the ROM, but it is highly recommended that this not be done as some graphics cards have used self modifying code for operation.

The following figure shows how all four bytes are mapped into PA-RISC memory mapped IO space. The area in gray depicts the valid data for each long word address.

| Byte 0 | Byte 1 | Byte 2 | Byte 3 | Address |

|--------|--------|--------|--------|---------|

| 0x11   | 0x22   | 0x33   | 0x44   | 0x0     |

| 0x55   | 0x66   | 0x77   | 0x88   | 0x4     |

| 0x99   | 0xaa   | 0xbb   | 0xcc   | 0x8     |

| 0xdd   | 0xee   | Oxff   | 0x01   | Охс     |

| 0x02   | 0x03   | 0x04   | 0x05   | 0x10    |

|        |        |        |        |         |

| 0xfa   | 0xfb   | Oxfc   | Oxfd   | end Rom |

## Figure 4 - Word Mode ROM

Note that in the figure if you perform a long word read of address 0x0 you would get 0x11223344 because all four bytes are mapped.

## 4.1.3 **PCI**

The PCI Local Bus Architecture defines an Expansion ROM. It describes the header format to be used in the Expansion ROM images on the PCI cards.

#### 4.1.3.1 Multiple ROM Images in a PCI ROM

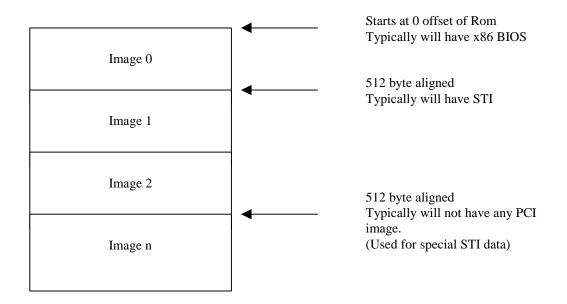

The PCI architecture allows for multiple ROM images in a single physical ROM as shown in the following figure. In addition, there is nothing to prohibit code supporting different architectures (x86 and PA-RISC) or supporting different operating systems (DOS and HP-UX).

Figure 5 - PCI ROM Image

## 4.1.3.2 Details of a single ROM image

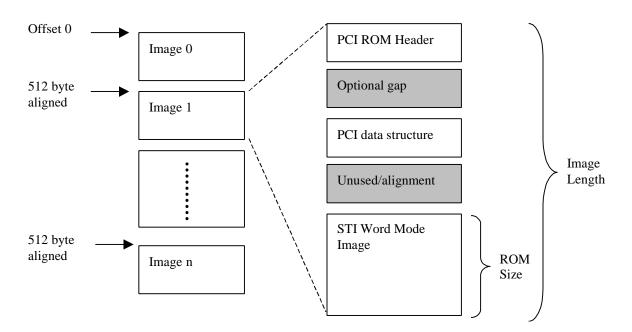

This document concerns STI and not x86 BIOS so we will focus on the details of what an STI image in a PCI ROM would look like. In the figure below you can see the basic organization of the parts of PCI Image and how they relate to STI. The normal WORD MODE STI image is not changed, it is just appended to the PCI ROM Header and the PCI data structure.

Figure 6 - STI Image in PCI Rom

#### 4.1.3.3 PCI ROM Header Details

Note that all offsets are offsets from the beginning of the PCI ROM Header to the first valid byte of the structure to which they point.

The code format for PA-RISC code will be **BIG ENDIAN**. The PCI header and PCI Data Structures will be **LITTLE ENDIAN**.

Below is the format of the PCI Header with HP unique fields added.

Note: Little Endian Format

| Byte 3       | Byte 2        | Byte 1    | Byte 0   | Offset |

|--------------|---------------|-----------|----------|--------|

| 0            | 0             | 0xaa      | 0x55     | 0      |

| ROM Type     | 0             | 0         | 0        | 4      |

|              | STI Ima       | ge Offset |          | 8      |

| MSB          |               |           | LSB      | 0      |

| PCI Region N | Iapper Offset | ROM Size  |          | 0xc    |

| MSB          | LSB           | MSB       | LSB      | UXC    |

| 0            | 0             | 0         | 0        | 0x10   |

| 0            | 0             | 0         | 0        | 0x14   |

|              |               | PCI DS    | S Offset | 0.12   |

|              |               | MSB       | LSB      | 0x18   |

Figure 7 - PCI Header in Little Endian Format

Note: The shaded areas are architected by PCI 2.1, all other areas are HP Unique.

#### 4.1.3.3.1 Header – PCI Architected

The "55Aah" is the option ROM signature, which is a x86 BIOS legacy, and indicates this to be a valid PCI ROM.

## 4.1.3.3.2 ROM Type – HP Unique

This number is valid only when the "code type" byte in the PCI Data structure indicates the code to be of type "PA-RISC". See the details of the PCI DS.

Valid ROM Types are:

| 0 | = | Undefined ROM type image |

|---|---|--------------------------|

| 1 | = | STI ROM type image       |

| 2     | = | PA-RISC IODC type image (PA1.1)               |

|-------|---|-----------------------------------------------|

| 9-255 | = | <b>Reserved for future PCI HP-PA hardware</b> |

## 4.1.3.3.3 STI Image Offset – HP Unique

This is a 32 bit offset (in little endian format) from the beginning of the PCI ROM header to the first byte of the STI image.

## 4.1.3.3.4 ROM Size – HP Unique

This field indicates the size of the ROM. It is in multiples of 512 bytes.

## 4.1.3.3.5 PCI DS Offset – PCI Architected

This is a 16 bit offset (in little endian format) from the beginning of the PCI ROM header to the PCI Data Structure.

## 4.1.3.3.6 PCI Region Mapper Offset – HP Unique

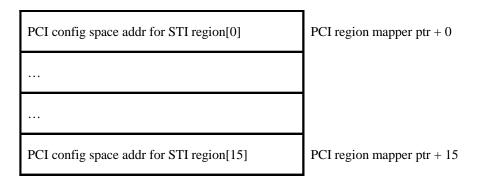

This is a 16 bit value that is an offset from the beginning of the ROM to the beginning of the PCI region mapper array. Below is a description of the pci region mapper array.

Figure 8 - PCI Region Mapper for STI

Each entry in the pci region mapper array is one byte. The value in each byte will be a pci config space offset. Normally this will be one of the pci bars, 0x10 for example. Unused entries contain 0.

To understand the need for this you will have to read the section on region mapper in the remaining document. STI breaks the physical card into 16 possible regions, each in a separate, non-contiguous space and the region mapper is the mechanism used to relate the pci bars to the STI regions.

Note that the STI dev region list is currently constrained to 8 entries but the pci region mapper can have up to 16 entries. This is for future expansion, currently the firmware and kernel only use 8 STI region entries, and so only the first 8 pci region mapper array entries will be used. The other 8 would contain 0.

The STI dev region list, as explained later, makes the assumption that the entries in the device region list are all offsets from the base of the card's hard physical address (HPA). This worked well for the SGC and GSC bus structures. But, for PCI, this was not sufficient. The PCI architecture lets you map various parts of the hardware basically anywhere you want, and it does this through the PCI BAR mechanism. Since STI has made the assumption that all regions are offset from the start of the hardware, the PCI region mapper was invented. This allows each individual STI device region to be an offset from a particular PCI BAR entry, and not from the base of the hardware.

## 4.1.3.3.7 PCI Data Structure – PCI Architected

There are no changes from the standard PCI Data Structure definition. The only addition is the PA-RISC code type assigned by PCISIG. The following code types are valid:

| 0    | = | Intel x86 PC-AT compatible code |

|------|---|---------------------------------|

| 1    | = | <b>Open Firmware for PCI</b>    |

| 0x10 | = | HP PA-RISC code                 |

Note: The PCI Spec Revision 2.2 (Dec 18, '98) indicates that 2 is assigned to HP PA-RISC code but this is incorrect. They assigned 0x10 (or maybe they assigned 2 but told us the wrong value), in any case, to work properly with System firmware and HP-UX kernel you must use 0x10 in this field.

See the PCI spec for further details.

Note: Little Endian Format

| Byte 3            | Byte 2             | Byte 1         | Byte 0    | Offset |

|-------------------|--------------------|----------------|-----------|--------|

| "R" (52h)         | " <b>I</b> " (49h) | "C" (43h)      | "P" (50h) | 0      |

| Device ID         |                    | Vendor ID      |           | 4      |

| PCI DS            | Length             | Pointer to VPD |           | 8      |

| MSB               | LSB                | MSB            | LSB       |        |

| Class Code DS Rev |                    |                |           | 0xc    |

| Code Rev Level    |                    | Image Length   |           | 0x10   |

| MSB               | LSB                | MSB            | LSB       |        |

| 0                 | 0                  | Indicator      | Code Type | 0x14   |

Figure 9 - PCI Data Structure

Note: All fields are architected by PCI spec rev 2.1

#### 4.1.3.4 PCI dual EROM mapping

For SGC and GSC based graphics cards, the STI ROM must be available at the base HPA. For PCI based cards the STI ROM must be accessible through the PCI expansion ROM space and optionally, the base HPA. There is no longer a requirement to have the STI ROM available at the base HPA for PCI based devices, but this is SPU dependent and only the newer SPU will handle this.

#### 4.1.4 Aberrations

#### 4.1.4.1 Column mode

A word mode ROM accessed in a byte mode manner will yield a column mode ROM. Various data like fonts can be stored along the columns. The only reason this has been done in the past is when the hardware design was incorrect and did not properly decode the word mode ROM.

## 4.1.4.2 Romless (built into boot ROM)

Capability does exist to integrate the STI image with the BOOT ROM image, but this does require both FIRMWARE and OS (HP-UX) to agree on how access is made. This was done with the built in graphics on the 712 and on the later generation 715 and 725 products.

For these products, the firmware and kernel will find the pointer to the STI image at offset 0x604 in page zero. This is a 4 byte pointer to the location of the STI image within the BOOT ROM image.

#### 4.2 STI Image Format

#### 4.2.1 General

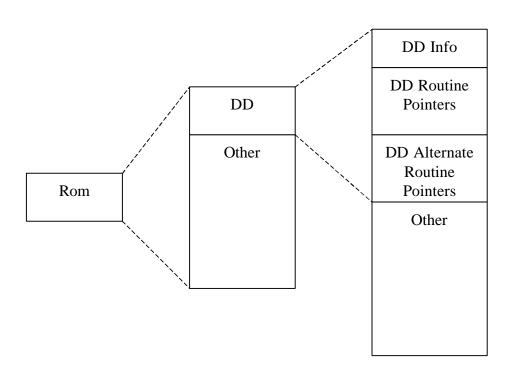

The STI ROM image is broken up into a Device Data section (which is architected) and the remainder of the ROM where all the routines, font tables live and various other useful parts.

Figure 10 - STI ROM Structure

Note: For PCI, this is the STI Word mode image part of figure 4. Otherwise, this is either the physical ROM on the card or the image of the STI in the boot ROM.

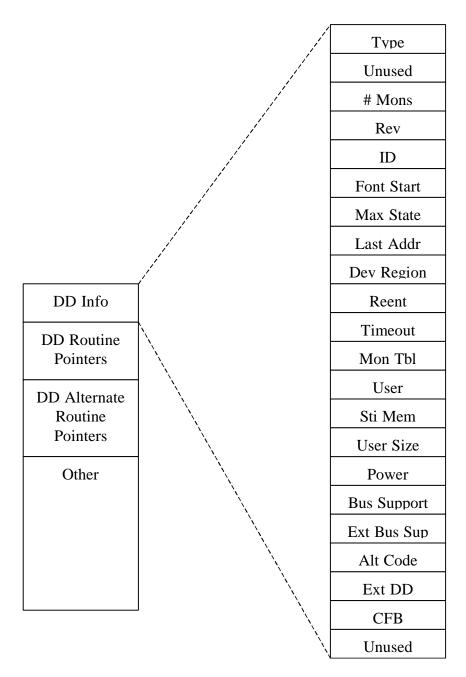

The Device Data (DD) section contains offsets to the various architected fields in the ROM, such as the different routines and the beginning of the font tables. And is typified in the following figure.

Figure 11 – DD Info Structure

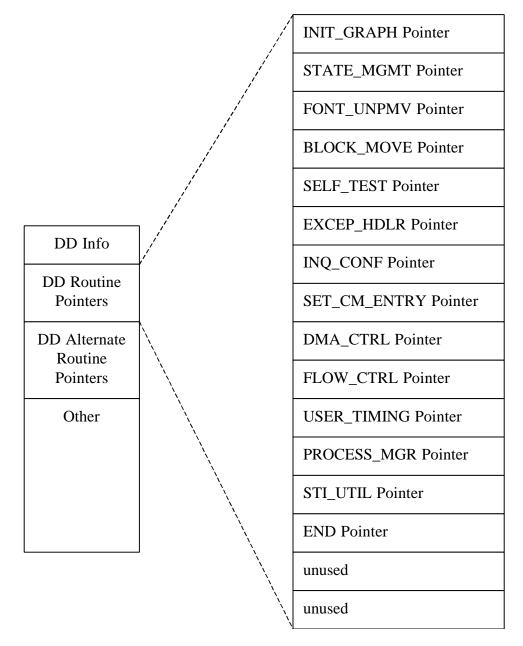

Figure 12 – Routine Structure

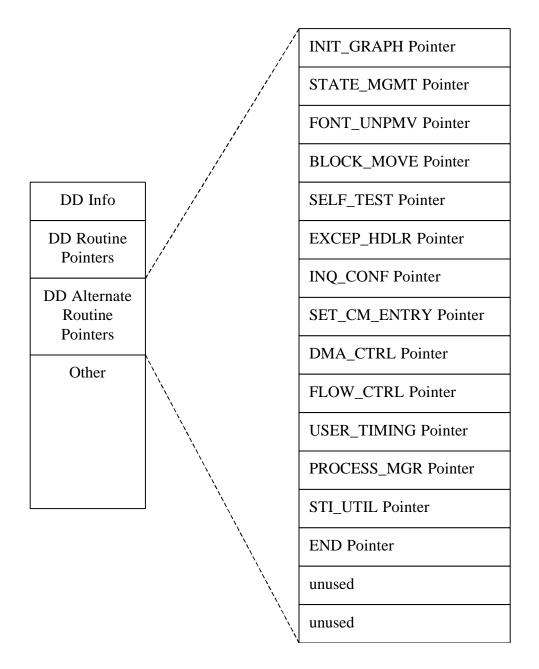

Figure 13 – Alternate Routine Structure

The beginning of the STI image contains the DD section. It contains information about the type of device present. A boot ROM searching for a graphics device would do so by reading byte 3 (LSB of the first word) at the low portion of each possible graphics device location STI ROM (base HPA for non PCI or PCI expansion ROM). A bus error would indicate no graphics device is present. If a graphics device is found in a given slot, self test must still be run on the device before it is used to insure that it is fully functional.

The initialization routine must be run both before and after any self test as self test can leave the device in an unknown state.

The addressing scheme in the STI ROM uses a format whereby addresses contained in the DD are all 32 bits and are byte counts relative to the starting address of the device. (For SGC devices all but the top (most-significant) 6 bits must contain zeroes.) The absolute location can be determined by the SPU by substituting the top 6 bits of the graphics board address (i.e., its SGC slot address) into the corresponding 6 bits of the address read from the DD.

NOTE: This is not true for PCI based systems. The older SGC and GSC based systems required the graphics to be at 0xf400000, 0xf6000000, 0xf8000000 or 0xfa000000. There is no such requirement on PCI based graphics.

It is assumed that the SPU will have a separate I/O space for devices with STI ROM's and will know that only such devices can exist there.

The DD uses 768 bytes of mapped byte mode ROM space. A tabular description of the complete DD section follows the description of each section.

| Field Name           | Word Mode<br>Address | Word Mode<br>Size (Bytes) | Byte Mode<br>Address | Byte Mode<br>Size (Bytes) |

|----------------------|----------------------|---------------------------|----------------------|---------------------------|

| Device Type          | 00                   | 1                         | -                    | -                         |

| Device Type          | 01                   | 1                         | -                    | -                         |

| Device Type          | 02                   | 1                         | -                    | -                         |

| Device Type          | 03                   | 1                         | 03                   | 1                         |

| Unused               | 04                   | 1                         | -                    | -                         |

| Number<br>Monitors   | 05                   | 1                         | 07                   | 1                         |

| Global Rom<br>Rev    | 06                   | 1                         | 0b                   | 1                         |

| Local Rom<br>Rev     | 07                   | 1                         | Of                   | 1                         |

| Graphics ID<br>(MSB) | 08                   | 8                         | 13                   | 8                         |

| Graphics ID          | 09                   |                           | 17                   |                           |

| Graphics ID0a1bGraphics ID0b1fGraphics ID0c23Graphics ID0d27Graphics ID0e2bGraphics ID0f2fFont Start104334Addr (MSB)104334Font Start1137Addr1137Font Start123bFont Start133fMax State144434Max State1547 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Graphics ID0c23Graphics ID0d27Graphics ID0e2bGraphics ID0f2fFont Start<br>Addr (MSB)104334Font Start<br>Addr1137Font Start<br>Addr123bFont Start<br>Addr133fMax State<br>(MSB)144434                     |

| Graphics ID0d27Graphics ID0e2bGraphics ID<br>(LSB)0f2fFont Start<br>Addr (MSB)104334Font Start<br>Addr1137Font Start<br>Addr123bFont Start<br>Addr133fMax State<br>Storage<br>(MSB)144434                |

| Graphics ID0e2bGraphics ID<br>(LSB)0f2fFont Start<br>Addr (MSB)104334Font Start<br>Addr1137Font Start<br>Addr123bFont Start<br>Addr133fMax State<br>Storage<br>(MSB)144434                               |

| Graphics ID<br>(LSB)Of2fFont Start<br>Addr (MSB)104334Font Start<br>Addr1137Font Start<br>Addr123bFont Start<br>Addr133fMax State<br>Storage<br>(MSB)144434                                              |

| (LSB)Font Start104334Addr (MSB)104334Font Start113737Addr123b3bFont Start123bAddr133fMax State144434Storage<br>(MSB)144434                                                                               |

| Addr (MSB)Font Start1137Addr123bFont Start123bFont Start133fMax State144434Storage<br>(MSB)144434                                                                                                        |

| AddrFont Start123bAddr133fFont Start133fAddr (LSB)144434Storage<br>(MSB)144434                                                                                                                           |

| AddrFont Start<br>Addr (LSB)133fMax State<br>Storage<br>(MSB)144434                                                                                                                                      |

| Addr (LSB)Max State144434Storage<br>(MSB)144434                                                                                                                                                          |

| Storage<br>(MSB)                                                                                                                                                                                         |

| <b>Max State</b> 15 47                                                                                                                                                                                   |

| Storage                                                                                                                                                                                                  |

| Max State164bStorage                                                                                                                                                                                     |

| Max State174fStorage (LSB)4f                                                                                                                                                                             |

| Rom Last         18         4         53         4           Addr (MSB)         4         53         4                                                                                                   |

| Rom Last         19         57           Addr         57                                                                                                                                                 |

| Rom Last1a5bAddr5b                                                                                                                                                                                       |

| Rom Last<br>Addr (LSB)        | 1b |   | 5f |   |

|-------------------------------|----|---|----|---|

| Device Region<br>List (MSB)   | 1c | 4 | 63 | 4 |

| Device Region<br>List         | 1d |   | 67 |   |

| Device Region<br>List         | 1e |   | бb |   |

| Device Region<br>List (LSB)   | 1f |   | 6f |   |

| Max Reent<br>Storage<br>(MSB) | 20 | 2 | 73 | 2 |

| Max Reent<br>Storage (LSB)    | 21 |   | 77 |   |

| Max Timeout<br>(MSB)          | 22 | 2 | 7b | 2 |

| Max Timeout<br>(LSB)          | 23 |   | 7f |   |

| Mon Table<br>Address<br>(MSB) | 24 | 4 | 83 | 4 |

| Mon Table<br>Address          | 25 |   | 87 |   |

| Mon Table<br>Address          | 26 |   | 8b |   |

| Mon Table<br>Address<br>(LSB) | 27 |   | 8f |   |

| User Data<br>Address<br>(MSB) | 28 | 4 | 93 | 4 |

| User Data<br>Address           | 29 |   | 97 |   |

|--------------------------------|----|---|----|---|

| User Data<br>Address           | 2a |   | 9b |   |

| User Data<br>Address<br>(LSB)  | 2b |   | 9f |   |

| STI Memory<br>Request<br>(MSB) | 2c | 4 | A3 |   |

| STI Memory<br>Request          | 2d |   | A7 |   |

| STI Memory<br>Request          | 2e |   | Ab |   |

| STI Memory<br>Request<br>(LSB) | 2f |   | Af |   |

| User Data<br>Size (MSB)        | 30 | 4 | B3 |   |

| User Data<br>Size              | 31 |   | B7 |   |

| User Data<br>Size              | 32 |   | Bb |   |

| User Data<br>Size (LSB)        | 33 |   | Bf |   |

| Power Usage<br>(MSB)           | 34 | 2 | C3 | 2 |

| Power Usage<br>(LSB)           | 35 |   | C5 |   |

| Bus Support                    | 36 | 1 | Cb | 1 |

| Extended Bus<br>Support        | 37 | 1 | Cf | 1 |

| Alternate<br>Code Type  | 38 | 1 | D3 | 1 |

|-------------------------|----|---|----|---|

| Extended DD<br>Struct 1 | 39 | 1 | D7 | 1 |

| Extended DD<br>Struct 2 | 3a | 1 | Db | 1 |

| Extended DD<br>Struct 3 | 3b | 1 | Df | 1 |

| CFB Address<br>(MSB)    | 3с | 4 | E3 |   |

| CFB Address             | 3d |   | E7 |   |

| CFB Address             | 3e |   | Eb |   |

| CFB Address<br>(LSB)    | 3f |   | Ef |   |

| Unused                  | -  | - | F3 | 4 |

| Unused                  | -  | - | F7 |   |

| Unused                  | -  | - | Fb |   |

| Unused                  | -  | - | Ff |   |

Figure 14 - DD Structure

# 4.2.2 DD Struct Field Descriptions

### 4.2.2.1 device type

The Device Type is included to cover the possibility that non-graphics devices may use the STI ROM spec in the future. Currently, the only defined device types are one for Byte mode ROM's and 3 for Word mode ROM's. Device type zero is, and must remain, unused.

Note that in byte mode ROM's, the device type is the first valid byte in the ROM which is the least significant byte of the first word. In word mode ROM's the least significant byte still contains the actual device type, but that type is also copied into the other 3 bytes of the first word.

Remember that in byte mode ROM's, the contents of the top 3 bytes are indeterminate. Sometimes they might show up as zero and other times not. Some bus controllers will actually return what ever was last in the bus latches, and other bus controllers might actually duplicate the least significant byte into the other three. So, be safe, in byte mode ROM's only use the least significant byte.

### 4.2.2.2 num mons

The num mons field identifies how many different monitor selections the STI image supports. This is typically used for supporting different resolution/refresh rate combinations. There is no requirement that STI support more than a single monitor type but customers expect the capability of using different monitors.

#### 4.2.2.3 global revisions

Including a global ROM revision number in the STI ROM makes it possible to identify the STI ROM spec revision that the ROM was generated from.

For instance, STI ROM spec revision 8.02 must use a 0x82 for the global revision in the ROM. The current version of the spec is 8.0d (8.13) so the Global revision in a ROM based on this spec would be 8.13.

The lower nibble in the global revision in the ROM will be converted to a two digit decimal number and will become the two decimal digits to the right of the decimal point. The upper nibble will be converted to a one or two digit decimal number (as appropriate) and become the decimal digit(s) to the left of the decimal point in the spec revision. For example, Global revision number 0xA3 will correspond to spec revision 10.03.

### 4.2.2.4 Local revisions

Including a Local ROM revision number in the STI ROM makes it possible to identify the various version of the ROM for each specific device. This field must start with revision zero and must be incremented whenever the ROM is changed. The local revision number should be used for such things as indicating that the code in the ROM has changed to fix a problem. STI code developers should maintain records regarding the significance of this revision level. This local revision number must be reset to zero whenever the global revision has been incremented.

#### 4.2.2.5 graphics id

The graphics ID has been allocated 64 bits to allow the ID to be assigned via a scheme similar to that in use at the Apollo Division. In addition, the most significant 32 bits of the ID will also be unique from device to device. Users who require a 32 bit ID should

use only the upper half of the ID while 64 bit ID users should use the entire ID. Note that the least significant 32 bits will not be unique between devices. Appendix A discusses the means by which ID's can be acquired.

# 4.2.2.6 font start

These 4 bytes contain a byte count to the first valid byte of the font storage area in STI ROM, relative to start of the STI ROM. All addresses in the font storage space are relative to the start of the font storage and need this value added to them to get absolute addresses. The STI ROM must provide at least one font although this font may vary in character size from device to device. An option is provided in the font storage area for adding additional fonts in ROM and providing a pointer to the start of the next font. As with all other areas of storage in the ROM, the font storage area only uses the least significant byte of each word.

# 4.2.2.7 Maximum state storage

This location contains the number of 32 bit words of RAM for state storage that must be made available to the state management routine if state will be saved and restored. The contents of this space must be preserved if a state needs to later be restored.

# 4.2.2.8 Last address of ROM

These four bytes contain the byte count to the last valid byte in the STI ROM, relative to the start of the STI ROM. This value is needed by the routine doing the CRC check of the ROM.

The values placed at the last two addresses are those which would set a CRC of the entire STI ROM space to zero.

The ROM's first valid word is at relative location 0x000000 of the graphics device's space, and the last valid word is at the "End of ROM Address". Special care must be taken to observe the ROM's single-byte width so only valid bytes are included in the CRC. For word mode ROM all 4 bytes are valid and must be included as part of the CRC.

Performing a CRC on the ROM using the algorithm described in Appendix B can test the STI ROM. A CRC is being used instead of a checksum, as it is able to detect more error conditions than a simple checksum. If the result is zero, the CRC is correct.

# 4.2.2.8.1 crc depends on ROM an even multiple of by es

# 4.2.2.9 dev region list

These four bytes contain a pointer to a table within the STI ROM. This table contains the necessary information to map the various regions of this device into virtual memory. The structure needed for this table is detailed in Appendix C. Each table entry contains the following data. Due to size limits in current kernel structure, this region list may contain a maximum of eight entries.

- A 14 bit value (offset) which indicates what the offset (in 4 Kbyte pages) is, from the start of the device's I/O space to the start of the region to be mapped.

- A one bit value indicating whether the user should be allowed access to this region (sys\_only=1) or not (sys\_only=0).

- A one bit value indicating whether this region should be mapped into data cache, if possible, (cache=1) or not (cache=0). If not possible, regions with this bit set should be mapped as uncached.

- A one bit value indicating whether this region should be mapped in using a block TLB if a block TLB is available (btlb=1) or not (btlb=0).

- A one bit value indicating whether this is the last region in the list (last=1) or not (last=0).

- A 14 bit value (length) which indicates how many 4 Kbyte pages must be mapped in for this block.

The region list structure in the STI ROM also contains a \*future ptr which can be used to expand the size or contents of the region list if needed in the future. This pointer must be the next entry after the last valid region entry and must be set to zero if unused.

By definition, region zero must be the STI ROM, region one must be the graphics device's framebuffer and region two must be the graphics device's control space. The STI ROM must exist. If either of two other regions does not exist, then the region list must contain an entry for that region but the offset and length fields must both be set to zero. Unused regions can exist in the table as valid regions but must be indicated by an entry of zero for the offset and length.

For example, if we have a very simple graphics device that contains only a STI ROM and framebuffer, the region list must contain the following data. The first entry contains the offset and length for the ROM region and the "last" bit cleared to indicate that it is not the last entry. The second entry contains the offset and length for the framebuffer and also has the "last" bit cleared to indicate that it is not the last entry. The third entry has a zero for both offset and length to indicate that there is nothing to map in for the control space. The third entry has the "last" bit set to indicate that this is the last entry. In this way, the table has indicated that we have three regions (the minimum required), but that only two of them have any space that needs to be mapped in.

All the other regions (to a maximum of eight total regions) are device dependent and their assignments must be defined in each device's External Reference Specification (ERS). Although this region list may have up to eight regions defined, the actual GCDESCRIBE, ioctl system call can only return a maximum of six device-dependent regions in a region list. The framebuffer and graphics control regions are returned as separate parameters. The translation between the region list used by the STI ROM and the region list returned by ioctl(GCDESCRIBE) is given below. The five device dependent regions must be organized such that the regions that can be mapped into user space are first, followed by the regions, two of which can be mapped into user space, then these two regions must be device dependent regions 1 and 2. The system region would then be device dependent region 3.

| Region Name      | STI Reg no. | GCDESCRIBE crt_region[N] |

|------------------|-------------|--------------------------|

| STI ROM          | 0           | 0                        |

| Framebuffer      | 1           | (crt_frame_base)         |

| Control Space    | 2           | (crt_control_base)       |

| Device Dep reg 1 | 3           | 1                        |

| Device Dep reg 2 | 4           | 2                        |

| Device Dep reg 3 | 5           | 3                        |

| Device Dep reg 4 | 6           | 4                        |

| Device Dep reg 5 | 7           | 5                        |

All the regions in the region list must have physically distinct addresses. That is, none of the regions may have the same or overlapping physical addresses.

Figure 15 – HP-UX Region Usage

This table is used by the calling process (e.g., kernel or boot ROM) by reading its contents and mapping each region into its memory space (virtual or physical), as appropriate. An array containing the addresses of the mapped in regions is then created and put into the glob conf structure by the calling routine. If any of the eight possible regions has not been mapped in, then that entry in the array must be null. In its simplest usage, the region array in the glob conf structure would be created from the region table

in the STI ROM as follows. The calling routine would take the 14 bit offset value from the ROM table and put it in the lower 14 bits of a 32 bit word. This value would then be shifted left 12 bits to change it from a 4 kbyte page count to a byte count. The starting address of this device's I/O space would then be added to this value to get the starting address of this region. This would be done for each of the valid regions in the ROM table.

The block TLB (see below) flag should be used in the following manner. The STI ROM developer should flag all regions that could significantly benefit from being mapped with a block TLB, with the btlb flag equal to one. STI ROM developers should consult with graphics driver developer and kernel developers to understand the best usage of block TLB's. Calling routines that are using the block TLB flag should implement the following algorithm for mapping in regions with block TLB's. The calling routine should first determine if the framebuffer (region 1) is marked for mapping with a block TLB. If so, the calling routine should scan all the other regions to identify those regions which are flagged for block TLB mapping and which exist in the same block TLB boundaries (e.g., 16Mbytes) as the framebuffer. The calling routine should then map in all these regions using the first available block TLB. If other block TLB's are available for use by this device, the calling routine should scan the remaining regions for those regions which are flagged for block TLB mapping but weren't mapped with the first block TLB. These regions should be grouped as was done for the first block TLB and then mapped. Note that the first block TLB should be used for the region containing the framebuffer. It is expected that few, if any, graphics devices will be able to effectively use more than two block TLB's and rarely will a device have access to more than two block TLB's.

#### 4.2.2.9.1 Block TLBs

New SPU/OS architectures are beginning to support a Translation Lookaside Buffer (TLB) which allows a block of a device's physical addresses to be mapped into virtual memory as a very large block rather than only in a 4kbyte blocks. There are significant performance advantages to mapping in a graphics device's I/O space in this manner but there are usually constraints that must be met to allow it to be done. For instance on PCX-S (the snakes chip set), in order for a 16 Mbyte block to be mapped into user space, it must be a contiguous block of user space and must be on a 16 Mbyte boundary. Hardware designers are strongly encouraged to discuss the planned memory map for their devices with the OS developers need to provide a regions list that will allow the kernel to conclude where it can create a large block out of several regions without having any device dependent information other than access to the region list in the STI ROM. This may require the size of certain regions in the regions list to be expand to include unused areas of the memory map.

#### 4.2.2.10 max reent

These two bytes contain the number of words which must be provided by the calling routine if any STI routines are asked to exit (WAIT=0) rather than busy wait. The save addr pointer in glob\_conf points to the start of this space. This space is global and therefore its contents must be preserved between repeated calls to an STI routine that has not completed. If the calling routine allows busy waiting (WAIT=1), then the save\_addr pointer must be null and no space is therefore provided.

### 4.2.2.11 max timeout

These two bytes contain a count of the maximum number of tenths of seconds which any of the STI routines could take from when it is started to when it would normally finish. This count should be used by calling routines to determine if the current STI routine has hung and should be aborted. Any STI routine that takes more than this time to complete should be considered as hung. It is expected that this timer value would be used with a hardware timer in the SPU that could issue an interrupt after the time had elapsed.

#### 4.2.2.12 mon tbl

For graphics devices that support multiple monitors this entry identifies the number of monitors supported.

#### 4.2.2.13 user data offset

Data that is used both by the STI firmware as well as user mode code can be located by using user data. This has typically been done for timing data so that user mode code such as SAM can access the timing parameters and display a dialog to the user on timing choices.

#### 4.2.2.14 sti mem request

Since each STI routine is independent of every other routine, it is sometimes necessary for routines to be able to pass data between themselves. This indicates the number of bytes required by STI. Note that current SPU firmware limits the maximum amount to 256 bytes, but the kernel has no such limitation.

#### 4.2.2.15 user data size

This is the size of the data pointed to by the user data offset.

### 4.2.2.16 Power Usage

Number of Watts (maximum) used by the graphics hardware. SPU firmware, as well as the kernel, to adjust internal fan speeds uses this value.

### 4.2.2.17 Bus support

The bus support byte contains various flags that indicate special support required for different bus architectures. Included below is the current definition for each of the bits.

#define BUS\_SUPPORT\_GSCINTL 0x01

#define BUS\_SUPPORT\_GSC15X 0x02

#define BUS\_SUPPORT\_GSC2X 0x04

#define BUS\_SUPPORT\_PCI\_IOEIM 0x08

#define BUS\_SUPPORT\_IMPLICIT\_LOCK 0x10

#define BUS\_SUPPORT\_PCI\_DUAL\_DECODE 0x20

#define BUS\_SUPPORT\_PCI\_EROM\_MMAP 0x40

#define BUS\_SUPPORT\_PCI\_STD\_INT 0x80

The GSCINTL is a representation that the card supports pulling the INTL line on the GSC bus to indicate an interrupt.

The GSC15X indicates the card supports the GSC1.5X spec, and the GSC2X indicates the card supports the GSC2X spec.

The PCI\_IOEIM indicates the card will use the PA-RISC directed interrupt mechanism that will write specific data (eim\_data) to a targeted processor at address (eim\_addr).